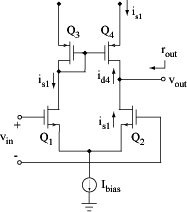

Consider a differential-input, single-ended-output MOS gain stage shown in the following figure:

Suppose the following dimensions and parameters of the MOS structure:

All transistors have the same gate width to length ratio W/L = (100 μm) / (1.6 μm),

Mobility of electrons near the silicon surface μn = 0.05 m2V-1s-1,

Gate capacitance per unit area Cox = 1.9 10-3 pF μm-2,

Transistor threshold voltage Vtn = 0.8 V,

Small-signal drain-source resistance rDS = 8 106 L / ID,

Bias current Ibias = 200 μA.

- Find the output impedance rout.

- Find the gain from the differential input Vin to the output Vout.

With the help of tutorials and recommended literature, perform the task demanded. |